1. Jurnal [Kembali]

2. Alat dan Bahan [Kembali]

4. Prinsip Kerja Rangkaian [Kembali]

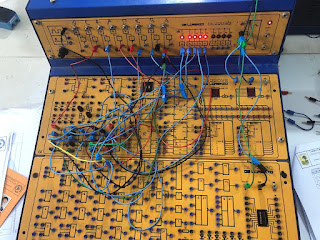

Pada percobaan 1 ini dirangkai suatu rangkaian Shift Register (register geser) keluaran output 4 bit dengan perwakilan output logicprobe. Pada rangkaian shift register keluaran 4 bit ini berarti menggunakan 4 buah IC J-K flip flop sebagai perwakilan 1 bit keluaran untuk 1 buah J-K flipflop.

Pada rangkaian ini memiiki 4 input masukan dari J-K flip flop dan 4 input keluaran dari J-K flip flop dimana akan terjadi proses operasi SISO, SIPO, PISO, dan PIPO pada rangkaian sesuai pengaturan switch dan kondisi.Maka padaprosesnya akan terjadi sistem kerja serial dan paralel yang dimana pada rangkaian akan terjadi perwakilan dari penggeseran pada sistem serial maupun serempak pada sistem paralel baik itu masukan maupun keluaran suatu biner yang dimana pergeseran maupun serempak pada sistem serial dan paralel ini akan mewakili MSB dan LSB dari 4 bit binner masukan dan keluaran. Terjadinyam proses input dan output logika pada rangkaian ini juga berarti bahwa proses terjadinya register geser ini dapat menyimpan memori sementara pada masukan menuju keluaran bit ke-4 dari dearah lingkup keluaran 4 bit.

5. Vidio Rangkaian [Kembali]

6. Analisa [Kembali]

a. Analisa output yang dihasilkan tiap-tiap kondisi!

-Kondisi 1: Ketika B3-B6 dan B0,B2 = 1 serta B1= X

didapati output yang dihasilkan yaitui 1011 keluar secara bergantian dan masuknya pun juga bergantian, sehingga shift register kondisi ini berjenis SISO

-Kondisi 2: Ketika B3-B6, B1= X B0=1 dan B2= ↓

didapati output yang dihasilkan yaitui 1011 keluar secara bergantian namun untuk outputnya keluar secara bersamaan, sehingga shift register kondisi ini berjenis SIPO

-Kondisi 3: Ketika B3-B6= X, B1=0, dan B0,B2=1

didapati output yang dihasilkan yaitui 1011 keluar secara bersamaan namun outputnya keluar secara bergantian, sehingga shift register kondisi ini berjenis PISO

-Kondisi r: Ketika B3-B6=X, B0=1 dan B1,B2=0

didapati output yang dihasilkan yaitui 1011 keluar secara bersamaan dan masuknya pun juga bersamaan, sehingga shift register kondisi ini berjenis PIPO

b. Jika gerbang AND pada rangkaian dihapus, sumber clock dihubungkan langsung ke flip flop, bandingkan output yang didapat

-Gerbang AND terhubung kepada switch B2 yang dapat memberhentikan jalannya data disaat memindah dan mentransfer data, maka ketika gerbang AND dihapus dna diganti CLK maka kita tidak bisa memberhentikan perpindahan atau tranfer data tersebut

0 Comments

Posting Komentar